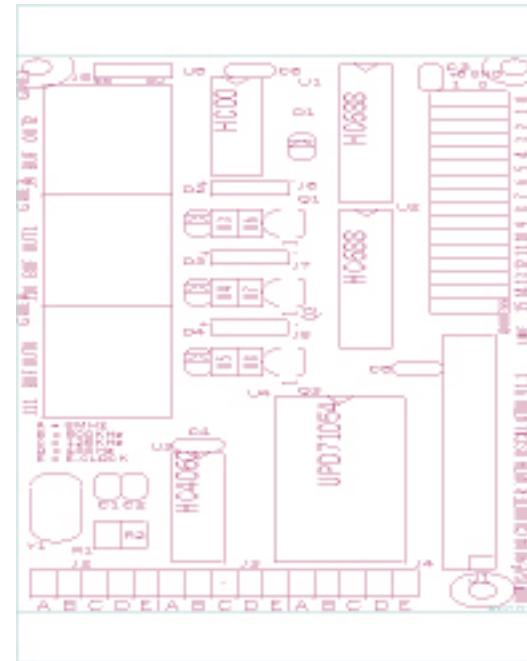

# NMIS/L-9004 3CH 16BIT Counter Card

The NMIS/L-9002, in 2X4"s format, provides a JEDSTACK computer system with access to three channels of 16-bit counters.

## FEATURES

- uPD71054 CMOS counter chip with:

- Three independant 16-bit counters

- Six programmable counter modes

- Binary or BCD counting

- Multiple latch command

- Wide clock rate from DC to 8 Mhz

- Low-power standby mode

- CMOS technology

The uPD71054 is a high-performance, programmable counter for system timing control. Three 16-bit counters, each with its own clock input, and OUT pin, can be clocked from D to 8 Mhz. Under software control, the uPD71054 can generate accurate time delays.

The uPD71054 contains three counters capable of binary, or BCD, operation. There are six programmable count modes. The counters operate independently and each can be set to a different mode.

After initialization, the uPD71054 can count the delay, and generate an interrupt when the task is complete, without further CPU intervention. This eliminates the need for software timing loops and frees the CPU for other tasks.

A Vertical Stacking Connector in the lower right hand corner (top view) provides connections to the processor's address and data bus, control signals, 5V power and ground. Address decoding of the drivers' space in memory is accomplished by two octal comparators and 16 two-position jumpers. Each jumper setting corresponds to the state of a particular address line. The NMIS/L-9004 occupies 4 address locations. Any 4-byte boundary in the 64K address space of the JEDSTACK processor's bus can be selected by the correct jumper placement.

## Description

Internally the three counter channels consist of a number of registers. The Command Register is an 8-bit register which is written with the control command determining the operating mode of the counter. The contents of this register cannot be read directly. (The multiple latch command, however, allows you to read the mode and status of each counter.) Binary or BCD operation can be selected, as well as the Count Mode (0-5), the Read/Write Mode, and the counter or counters involved.

Internally the three counters each have three 16-bit registers: the Counter itself, the Count Register, and the Count Latch. The Counter is a 16-bit down counter. The 16-bit Count Register can preset the 16-bit Counter by transferring the desired value to it. The 16-bit Count Latch can capture the Counter, and hold the data for processor access.

be